C++/SystemC-Based High-Level Synthesis for Faster, Smarter Hardware Design

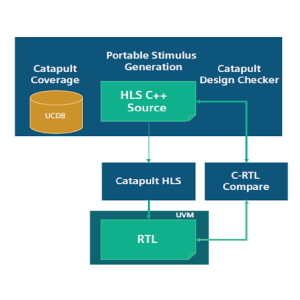

Catapult High-Level Synthesis (HLS) enables rapid hardware design by allowing developers to describe functionality in C++ or SystemC and automatically generate optimized RTL. Ideal for AI/ML, DSP, and complex SoC applications, Catapult dramatically shortens development cycles, enhances design quality, and accelerates time-to-market.

Key Highlights:

- High-Level Abstraction – Design with C++ or SystemC to boost productivity and enable rapid prototyping.

- Automated RTL Generation – Converts high-level descriptions into optimized, synthesis-ready Verilog/VHDL.

- PPA-Optimized Results – Built-in optimization ensures RTL meets power, performance, and area requirements.

- Architecture Exploration – Allows fast iterations of design structures to evaluate trade-offs early.

- Domain-Specific Support – Tailored features for AI, ML, image processing, and DSP-intensive designs.

- Integrated Debugging – Waveform-level and schematic debugging at both HLS and RTL levels.

- Interface Synthesis – Supports standard interfaces like AXI, AHB, and custom bus protocols.

- System-Level Integration – Works with SystemC TLM and virtual platforms for early software co-design.

- Simulation & Synthesis Ready – Produces high-quality RTL that integrates smoothly into traditional flows.

- Accelerates Time-to-Implementation – Shortens development time and reduces design risk through automation.