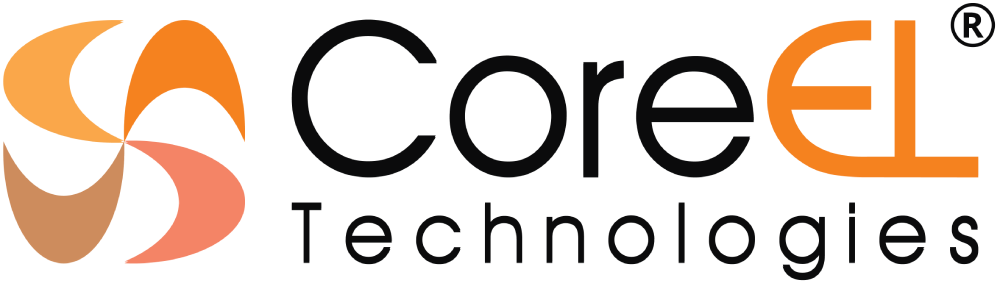

Automated, exhaustive CDC verification

Questa CDC from Siemens EDA is a formal verification tool that identifies and resolves critical clock-domain crossing (CDC) issues in multi-clock designs. With early detection and intelligent visualization, it helps ensure functional correctness and silicon success — without requiring formal verification expertise.

Key Features:

- Automated CDC Detection – Identifies chip-killing CDC violations directly from RTL, UPF, and constraint files.

- Metastability Risk Analysis – Flags unsafe synchronizers and vulnerable data paths across asynchronous domains.

- No Formal Expertise Needed – Runs exhaustive formal checks without requiring PSL/SVA property knowledge.

- Comprehensive Rule-Based Engine – Applies proven CDC verification rules to catch errors early in the design flow.

- Advanced Visualization Tools – Graphically traces CDC paths and violations, simplifying debug.

- UPF-Aware Verification – Interprets power intent to analyze CDC interactions in low-power designs.

- Part of the Siemens Flow – Integrates seamlessly with QuestaSim, Visualizer, and other Siemens tools.

- Early Signoff Confidence – Verifies CDC correctness before simulation, reducing late-stage surprises.

- Input Support – Accepts RTL (.v, .sv, .vhd), SDC/UPF constraints, and IP-based designs.